# HP 82000 IC Evaluation System Using the EDA Interface

# Models D50, D100, D200 and D400

SERIAL NUMBERS

This manual affects all instruments.

HP Part No. E1299-90001 Microfiche Part No. E1299-95001 Printed in West Germany November 1993

**Revision 2.0**

# Legal Information

## Notice

The information in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MANUAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or direct, indirect, special, incidental or consequential damages in connection with the furnishing, performance, or use of this manual.

## Warranty

A copy of the specific warranty terms applicable to your Hewlett-Packard product and replacement parts can be obtained from your local Sales and Service Office.

HILO-3 is a registered trademark of GenRad Inc. QuickSim is a registered trademark of Mentor Graphics Corporation Logician is a registered trademark of Daisy Systems Corporation

© Hewlett-Packard GmbH 1989

# **Printing History**

New editions of this manual will incorporate all material updates since tha previous edition. Update packages may be issued between editions and contain replacement and additional pages to be merged into the manual by the user. Each updated page will be indicated by a revision date at the bottom of the page. A vertical bar in the margin indicates the changes on each page. Note that pages which are rearranged due to changes on a previous page are not considered revised.

The manual printing date and part number indicate its current edition. The printing date changes when a new edition is printed. (Minor corrections and updates which are incorporated at reprint do not cause the date to change.) The manual part number changes when extensive technical changes are incorporated.

Revision 1 May 1989.

Effective Pages: ALL

Revision 2 November 1993

Effective Pages: ALL

# **Documentation Map**

The following figures show the manuals provided for the HP 82000 IC Evaluation System. For more information on the contents of each manual and a list of tasks, refer to the Documentation Roadmap booklet.

# Preface

## Purpose

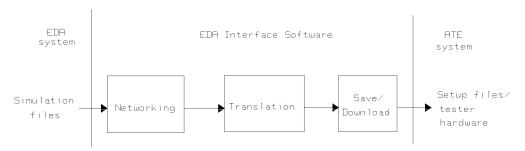

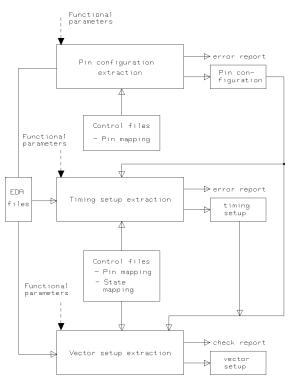

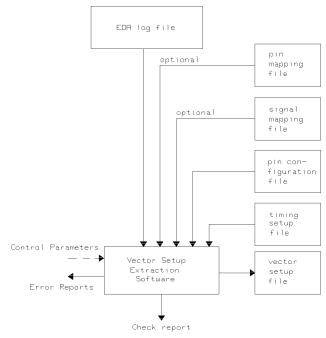

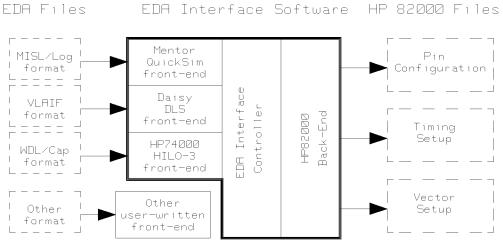

The purpose of this manual is to describe how to use the EDA Interface software to translate simulator files, generated on EDA stations, to functional tests that can be used to test devices on the HP 82000 IC Evaluation System.

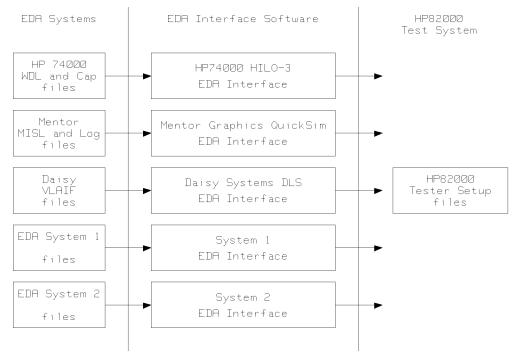

Simulation files from the following IC simulators can be processed:

- HP74000 HILO-3 simulator

- Mentor Graphic Corporation's QuickSim simulator

- Daisy Systems Daisy Logic Simulator

#### Audience

This manual is intended for engineers who want to test devices using functional tests translated from simulation files.

Before using this manual, you should have attended an HP82000 training course or worked through the EDA Interface section of the Getting Started Manual. If you have not already done so, work through this section now to get an understanding of the EDA Interface functions.

For information on writing your own translators, refer to the EDA Interface Programming Manual.

### Contents

This manual contains 11 chapters.

| 1       | Introduction - explains the purpose and use of the EDA<br>Interface software.                                |

|---------|--------------------------------------------------------------------------------------------------------------|

| 2       | Using the EDA Interface - how to setup and translate EDA files.                                              |

| 3       | Generating Control Files - how to set up control files to define<br>pin and state mapping                    |

| 4 to 7  | Extraction Software Descriptions - how the different parts of the software work and default values           |

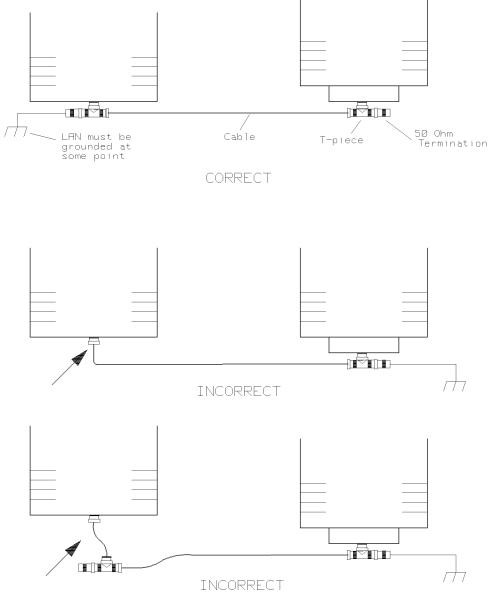

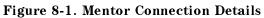

| 8       | System Networking Tools - describes how to make connections to, and communicate with other computer systems. |

| 9 to 11 | Descriptions of the standard formats supported by the EDA<br>Interface software.                             |

| А       | Description of the pin mapping file format                                                                   |

| В       | Description of the signal mapping file format                                                                |

| С       | Example EDA Files                                                                                            |

٧

# Conventions used in this manual

In the descriptions in this manual the following terms are used:

| pin mapping      | the mapping of EDA signals to physical tester pins                  |

|------------------|---------------------------------------------------------------------|

| pin name         | name of a tester pin                                                |

| signal mapping   | the mapping of waveform states to tester states                     |

| signal name      | name of a signal in an EDA file                                     |

| simulation files | files generated by a simulator that describe the behavior of device |

| waveform         | description of a signal in an EDA file                              |

| 1.         | What is the EDA Interface?                       |

|------------|--------------------------------------------------|

|            | Introduction                                     |

|            | Supported EDA Systems                            |

|            | EDA Interface Functionality                      |

| <b>2</b> . | Using the EDA Interface Software                 |

|            | Pre-Requisites                                   |

|            | Starting the PWS Software                        |

|            | Transferring the EDA Files                       |

|            | Starting the EDA Interface Software              |

|            | Selecting the EDA System                         |

|            | Selecting the EDA Interface Functions            |

|            | EDA Interface Status                             |

|            | Setting Up the EDA Interface                     |

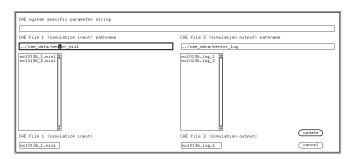

|            | Selecting the EDA files                          |

|            | Selecting the Path Name                          |

|            | Selecting EDA Files                              |

|            | Entering an EDA System-specific Parameter String |

|            | Selecting ATE Setup Files                        |

|            | Selecting a Pin Configuration                    |

|            | Selecting a Timing Setup File                    |

|            | Selecting a Vector Setup File                    |

|            | Leaving the ATE File Window                      |

|            | Selecting Control Files                          |

|            | Selecting the Pin Mapping Control File           |

|            | Selecting the State Mapping Control File         |

|            | Leaving the Control File Selection Window        |

|            | Setting Translation Options                      |

|            | Setting the Clock Period for the Translation     |

|            | Setting Pin Configuration Options                |

|            | Setting Timing Setup Extraction Options          |

|            | Update Pin Configuration                         |

|    | Timestamps to be Processed .                          |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 2-12 |

|----|-------------------------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|

|    | Vector Setup Extraction Options                       |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 2-12 |

|    | Check Waveforms                                       |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 2-13 |

|    | Generate Vector Setup                                 |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 2-13 |

|    | Timestamps to be Processed .                          |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 2-13 |

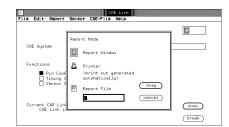

|    | Selecting the $\operatorname{Report}$ Mode $\ldots$ . | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 2-13 |

| 3. | Generating Control Files                              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |      |

|    | State Mapping                                         |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3-1  |

|    | Purpose of State Mapping                              |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3-1  |

|    | Starting the State Mapping Editor .                   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3-2  |

|    | Using the State Mapping Editor                        |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3-3  |

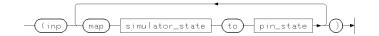

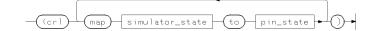

|    | Mapping Simulator States                              |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3-3  |

|    | Setting the System Inaccuracy                         |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3-4  |

|    | Saving the Signal Mapping File                        |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3-4  |

|    | Pin Mapping File                                      |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3-5  |

|    | Starting the Pin Mapping Editor .                     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3-5  |

|    | Generating a Pin Mapping file                         |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3-5  |

|    | Entering the Simulation Signal Na                     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3-5  |

|    | Entering the Signal Use                               |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3-5  |

|    | Entering the Tester Pin Name .                        |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3-6  |

|    | Entering the Tester Pin Type                          |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3-6  |

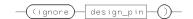

|    | Selecting Pins to Ignore                              |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 3-6  |

|    | Saving the Pin Mapping File                           | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 3-7  |

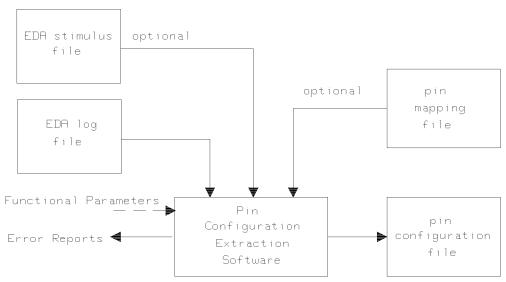

| 4. | Pin Configuration Extraction                          |   |   |   |   |   |   |   |   |   |   |   |   |   |   |      |

|    | Translation without a Pin Mapping File                | ) |   |   |   |   |   |   |   |   |   |   |   |   |   | 4-3  |

|    | Default Pin Mapping                                   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 4-3  |

|    | Signal Name to Pin Name Mapping                       |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 4-3  |

|    | Example                                               |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 4-3  |

|    | Unique Naming                                         |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 4-4  |

|    | Example                                               |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 4-4  |

|    | Signal Type to Pin Type Mapping .                     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 4-4  |

|    | Translation with a Pin Mapping File .                 |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 4-5  |

|    | Signal Name to Pin Name Mapping                       |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 4-5  |

|    | Combining Signals to make Pins                        |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 4-5  |

|    | Signal Type to Pin Type Mapping .                     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 4-6  |

|    | Ignore Signals                                        |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 4-7  |

|    | Example                                               |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 4-7  |

|    | Order of Pin Mapping Evaluation .                     |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 4-8  |

| 5. | Introduction to Timing and Vector ExtractionSignal Waveform Processing5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-1        |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-2        |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -2         |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-3        |

|    | F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-3        |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | , <i>3</i> |

|    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | , J<br>5-3 |

|    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-3        |

|    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-3        |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | , 0        |

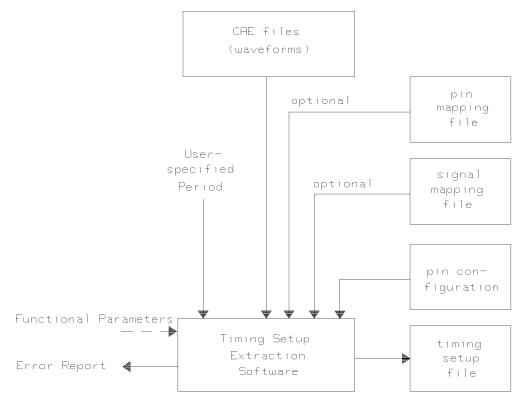

| 6. | Timing Setup Extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

|    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-3        |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -3         |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -4         |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-4        |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-4        |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-5        |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-5        |

|    | Timing Setup Defaults    6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -6         |

| 7. | Vector Extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>-</b> 2 |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -2         |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-3        |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-4        |

|    | ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | '-4        |

|    | OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | '-4        |

|    | Generate Vector Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -7         |

|    | Timestamps Processed by Vector Setup Extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-7        |

|    | Vector Setup Defaults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -8         |

| 8. | System Networking Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

|    | observation and the observation of the test of tes | -1         |

|    | Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-1        |